# LME49600 High-Performance, High-Fidelity, High-Current Headphone Buffer

Check for Samples: LME49600

#### **FEATURES**

- Pin-Selectable Bandwidth and Quiescent Current

- Pure Fidelity, Pure Performance

- Short Circuit Protection

- Thermal Shutdown

- TO–263 Surface-Mount Package

#### **APPLICATIONS**

- Headphone Amplifier Output Drive Stage

- Line Drivers

- Low Power Audio Amplifiers

- High-Current Operational Amplifier Output Stage

- ATE Pin Driver Buffer

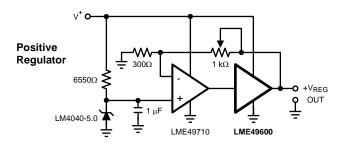

- Power Supply Regulator

#### DESCRIPTION

The LME49600 is a high performance, low distortion high fidelity 250mA audio buffer. The LME49600 is designed for a wide range of applications. It can be used inside the feedback loop of op amps.

The LME49600 offers a pin-selectable bandwidth: a low current, 110MHz bandwidth mode that consumes 7.3mA and a wide 180MHz bandwidth mode that consumes 13.2mA. In both modes the LME49600 has a nominal 2000V/ $\mu$ s slew rate. Bandwidth is easily adjusted by either leaving the BW pin unconnected or connecting a resistor between the BW pin and the V<sub>EE</sub> pin.

The LME49600 is fully protected through internal current limit and thermal shutdown.

#### **KEY SPECIFICATIONS**

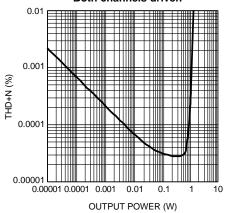

- Low THD+N (V<sub>OUT</sub> = 3V<sub>RMS</sub>, f = 1kHz, Figure 26): 0.00003% (typ)

- Slew Rate: 2000V/µs (typ)

- High Output Current: 250mA (typ)

- Bandwidth

- BW Pin Floating: 110MHz (typ)

- BW Connected to V<sub>EE</sub>: 180MHz (typ)

- Supply Voltage Range: ±2.25V ≤ V<sub>S</sub> ≤ ±18V

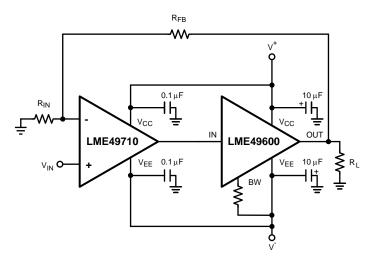

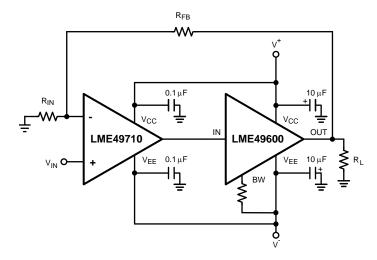

## **Typical Application Diagram**

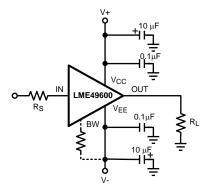

Figure 1. High Performance, High Fidelity LME49600 Audio Buffer Application

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

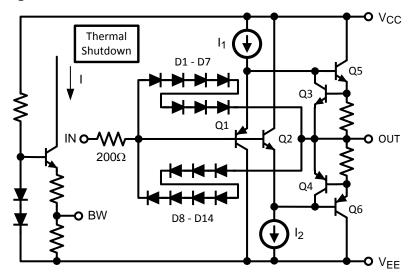

## **Functional Block Diagram**

Figure 2. Simplified Circuit Diagram (Note: I<sub>1</sub> and I<sub>2</sub> are mirrored from I)

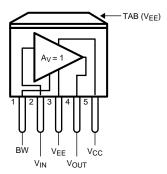

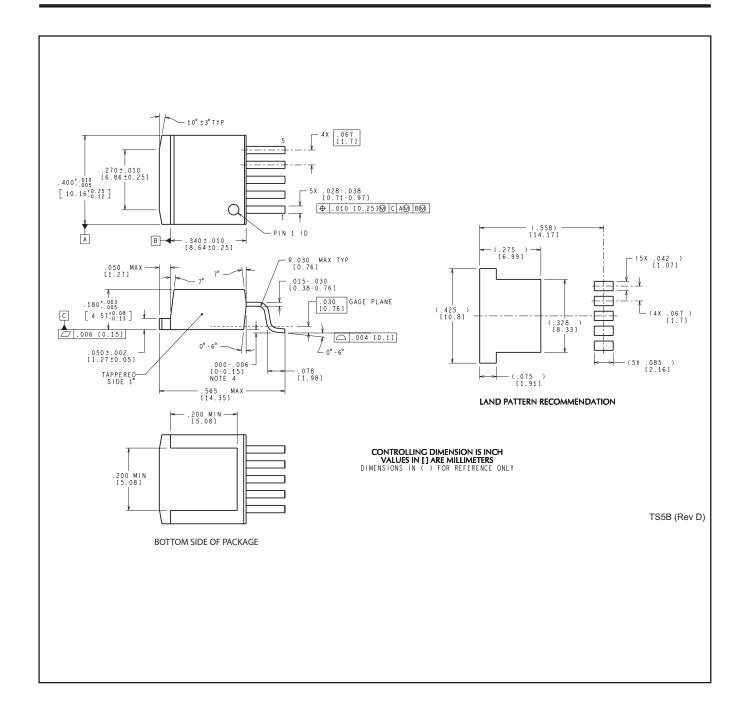

# **Connection Diagram**

The KTT package is non-isolated package. The package's metal back and any heat sink to which it is mounted are connected to the same potential as the  $-V_{\text{EE}}$  pin.

Figure 3. KTT Package (Top View) See Package Number KTT0005B

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ABSOLUTE MAXIMUM RATINGS**(1)(2)(3)

| Supply Voltage             |                             | ±20V   |

|----------------------------|-----------------------------|--------|

| ESD Ratings <sup>(4)</sup> | 2000V                       |        |

| ESD Rating <sup>(5)</sup>  | 200V                        |        |

| Storage Temperature        | -40°C to +150°C             |        |

| Junction Temperature       | 150°C                       |        |

| Thermal Resistance         | $\theta_{JC}$               | 4°C/W  |

|                            | $\theta_{JA}$               | 65°C/W |

|                            | $\theta_{JA}^{(6)}$         | 20°C/W |

| Soldering Information      | TO-263 Package (10 seconds) | 260°C  |

- (1) All voltages are measured with respect to ground, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not ensured for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) Human body model, 100pF discharged through a 1.5kΩ resistor.

- (5) Machine Model, 220pF 240pF discharged through all pins.

- (6) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub>-T<sub>A</sub>)/θ<sub>JA</sub> or the number given in Absolute Maximum Ratings, whichever is lower. For the LME49600, typical application (shown in Figure 26) with V<sub>SUPPLY</sub> = 30V, R<sub>L</sub> = 32Ω, the total power dissipation is 1.9W. θ<sub>JA</sub> = 20°C/W for the TO–263 package mounted to 16in<sup>2</sup> 1oz copper surface heat sink area.

#### OPERATING RATINGS<sup>(1)(2)</sup>

| Temperature Range | $T_{MIN} \le T_A \le T_{MAX}$ | -40°C ≤ T <sub>A</sub> ≤ 85°C |

|-------------------|-------------------------------|-------------------------------|

| Supply Voltage    |                               | ±2.25V to ±18V                |

(1) All voltages are measured with respect to ground, unless otherwise specified.

(2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not ensured for parameters where no limit is given, however, the typical value is a good indication of device performance.

#### SYSTEM ELECTRICAL CHARACTERISTICS FOR LME49600

The following specifications apply for  $V_S = \pm 15V$ ,  $f_{IN} = 1kHz$ , unless otherwise specified. Typicals and limits apply for  $T_A = 1kHz$

| Symbol                                 | Parameter                                                                             | Conditions                                                                                                                                                                   | LME4                                                                 | Units                                                                |                                     |  |

|----------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|--|

| Syllibol                               | Farameter                                                                             | Conditions                                                                                                                                                                   | Typical <sup>(1)</sup>                                               | Limit <sup>(2)</sup>                                                 | (Limits)                            |  |

| I <sub>Q</sub> Total Quiescent Current |                                                                                       | I <sub>OUT</sub> = 0<br>BW pin: No connect<br>BW pin: Connected to V <sub>EE</sub> pin                                                                                       | 7.3<br>13.2                                                          | 10.5<br>18                                                           | mA (max)<br>mA (max)                |  |

| THD+N                                  | Total Harmonic Distortion + Noise <sup>(3)</sup>                                      | $\begin{array}{l} A_V = 1, \ V_{OUT} = 3V_{RMS}, \ R_L \\ = 32\Omega, \ BW = 80kHz, \\ \text{closed loop see Figure 26.} \\ \text{f} = 1kHz \\ \text{f} = 20kHz \end{array}$ | 0.000035<br>0.0005                                                   |                                                                      | %<br>%                              |  |

| SR                                     | Slew Rate                                                                             | $30 \le BW \le 180MHz$<br>$V_{OUT} = 20V_{P-P}, R_L = 100\Omega$                                                                                                             | 2000                                                                 |                                                                      | V/µs                                |  |

|                                        | Bandwidth                                                                             | $A_V = -3dB$ BW pin: No Connect $R_L = 100\Omega$ $R_L = 1k\Omega$                                                                                                           | 100<br>110                                                           |                                                                      | MHz<br>MHz                          |  |

| BW                                     | Bandwidii                                                                             | $\begin{array}{l} A_V = -3 dB \\ BW \ pin: \ Connected \ to \ V_{EE} \ pin \\ R_L = 100 \Omega \\ R_L = 1 k \Omega \end{array}$                                              | / <sub>EE</sub> pin 160 180                                          |                                                                      | MHz<br>MHz                          |  |

|                                        | Valtaga Najaa Danajtu                                                                 | f = 10kHz<br>BW pin: No Connect                                                                                                                                              | 3.0                                                                  |                                                                      | nV/√ <del>Hz</del>                  |  |

|                                        | Voltage Noise Density                                                                 | f = 10kHz<br>BW pin: Connected to V <sub>EE</sub> pin                                                                                                                        | Typical (1)                                                          |                                                                      | nV/√ <del>Hz</del>                  |  |

| t <sub>s</sub>                         | Settling Time                                                                         | $\Delta V = 10V$ , $R_L = 100\Omega$<br>1% Accuracy<br>BW pin: No connect<br>BW pin: Connected to $V_{EE}$ pin                                                               |                                                                      |                                                                      | ns<br>ns                            |  |

| $A_V$                                  | Voltage Gain                                                                          | $\begin{aligned} &V_{OUT}=\pm 10V\\ &R_L=67\Omega\\ &R_L=100\Omega\\ &R_L=1k\Omega \end{aligned}$                                                                            | 0.95                                                                 | 0.92                                                                 | V/V (min)<br>V/V (min)<br>V/V (min) |  |

| W                                      | Voltage Output                                                                        | Positive I <sub>OUT</sub> = 10mA I <sub>OUT</sub> = 100mA I <sub>OUT</sub> = 150mA                                                                                           | V <sub>CC</sub> -2.0                                                 | V <sub>CC</sub> -1.6<br>V <sub>CC</sub> -2.1<br>V <sub>CC</sub> -2.7 | V (min)<br>V (min)<br>V (min)       |  |

| V <sub>OUT</sub> Voltage Output        | Negative $I_{OUT} = -10\text{mA}$ $I_{OUT} = -100\text{mA}$ $I_{OUT} = -150\text{mA}$ | V <sub>EE</sub> +3.1                                                                                                                                                         | V <sub>EE</sub> +1.6<br>V <sub>EE</sub> +2.4<br>V <sub>EE</sub> +3.2 | V (min)<br>V (min)<br>V (min)                                        |                                     |  |

| I <sub>OUT</sub>                       | Output Current                                                                        |                                                                                                                                                                              | ±250                                                                 |                                                                      | mA                                  |  |

| I <sub>OUT-SC</sub>                    | Short Circuit Output Current                                                          | BW pin: No Connect<br>BW pin: Connected to V <sub>EE</sub> pin                                                                                                               |                                                                      | ±550                                                                 | mA (max)<br>mA (max)                |  |

| I <sub>B</sub>                         | Input Bias Current                                                                    | V <sub>IN</sub> = 0V<br>BW pin: No Connect<br>BW pin: Connected to V <sub>EE</sub> pin                                                                                       |                                                                      |                                                                      | μΑ (max)<br>μΑ (max)                |  |

| Z <sub>IN</sub>                        | Input Impedance                                                                       | $R_L = 100\Omega$<br>BW pin: No Connect<br>BW pin: Connected to $V_{EE}$ pin                                                                                                 |                                                                      |                                                                      | ΜΩ<br>ΜΩ                            |  |

| Vos                                    | Offset Voltage                                                                        |                                                                                                                                                                              | ±17                                                                  | ±60                                                                  | mV (max)                            |  |

| V <sub>OS</sub> /°C                    | Offset Voltage vs Temperature                                                         | 40°C ≤ T <sub>A</sub> ≤ +125°C                                                                                                                                               | ±100                                                                 |                                                                      | μV/°C                               |  |

Typical specifications are specified at 25°C and represent the parametric norm.

Tested limits are ensured to AOQL (Average Outgoing Quality Level).

This is the distortion of the LME49600 operating in a closed loop configuration with an LME49710. When operating in an operational amplifier's feedback loop, the amplifier's open loop gain dominates, linearizing the system and determining the overall system distortion.

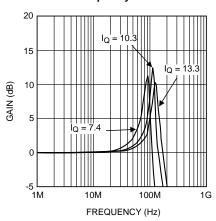

#### TYPICAL PERFORMANCE CHARACTERISTICS

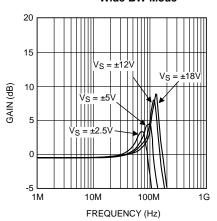

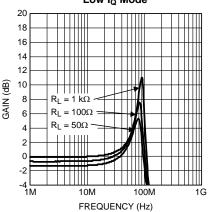

## Gain vs Frequency vs Quiescent Current

Figure 4.

# Gain vs Frequency vs Power Supply Voltage Wide BW Mode

Figure 6.

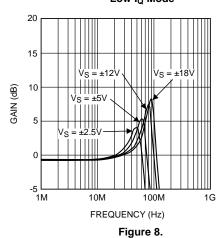

# Gain vs Frequency vs Power Supply Voltage Low $I_Q$ Mode

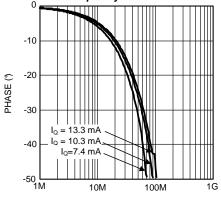

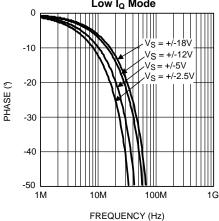

Phase vs Frequency vs Quiescent Current

FREQUENCY (Hz)

Figure 5.

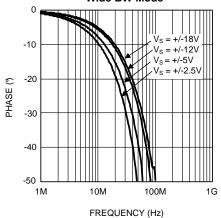

# Phase vs Frequency vs Supply Voltage Wide BW Mode

Figure 7.

#### Phase vs Frequency vs Supply Voltage Low I<sub>Q</sub> Mode

Figure 9.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

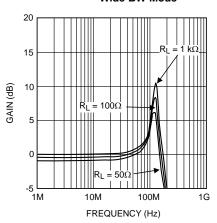

# $\begin{array}{c} \text{Gain vs Frequency vs R}_{\text{LOAD}} \\ \text{Wide BW Mode} \end{array}$

Figure 10.

# $\begin{array}{c} \text{Gain vs Frequency vs R}_{\text{LOAD}} \\ \text{Low I}_{\text{Q}} \ \text{Mode} \end{array}$

Figure 12.

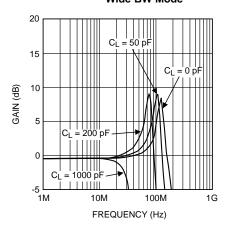

# Gain vs Frequency vs C<sub>LOAD</sub> Wide BW Mode

Figure 14.

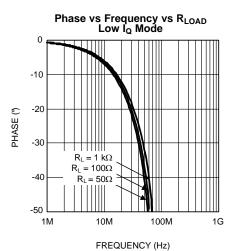

# Phase vs Frequency vs $R_{LOAD}$ Wide BW Mode 0 -10 -20 -40 $R_{L} = 1 \text{ k}\Omega$ $R_{L} = 100\Omega$ $R_{L} = 50\Omega$

FREQUENCY (Hz)

100M

1G

10M

-50

1M

Figure 11.

Figure 13.

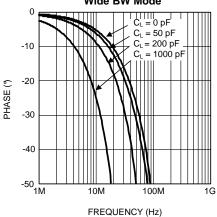

Phase vs Frequency vs C<sub>LOAD</sub> Wide BW Mode

Figure 15.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

# $\begin{array}{c} \text{Gain vs Frequency vs C}_{\text{LOAD}} \\ \text{Low I}_{\text{Q}} \ \text{Mode} \end{array}$ 20 15 GAIN (dB) $C_L = 0 pF$ $C_1 = 200 \text{ pF}$ $C_L$ -5 ∟ 1M

10M

Figure 16.

FREQUENCY (Hz)

100M

1G

Figure 18.

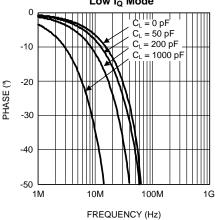

Phase vs Frequency vs  $C_{LOAD}$ Low  $I_Q$  Mode

Figure 17.

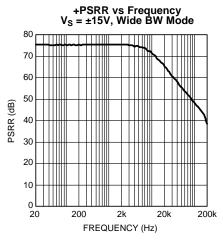

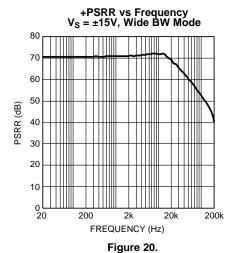

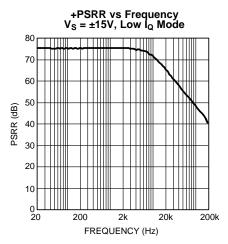

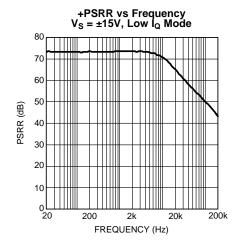

Figure 19.

Figure 21.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

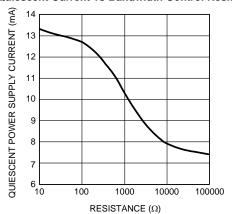

#### **Quiescent Current vs Bandwidth Control Resistance**

Figure 22.

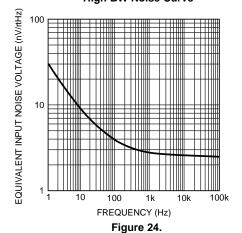

#### **High BW Noise Curve**

THD+N vs Output Voltage  $V_S = \pm 15V$ ,  $R_L = 32\Omega$ , f = 1kHz Both channels driven

Figure 23.

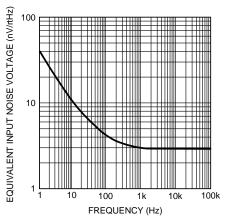

#### **Low BW Noise Curve**

Figure 25.

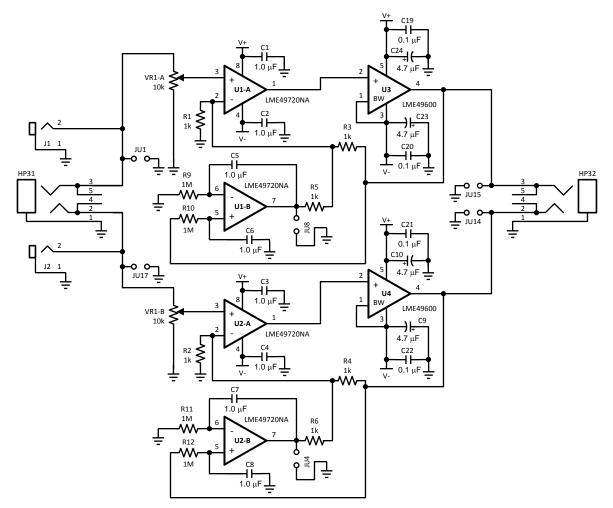

#### TYPICAL APPLICATION DIAGRAM

Figure 26. High Performance, High Fidelity LME49600 Audio Buffer Application

#### **DISTORTION MEASUREMENTS**

The vanishingly low residual distortion produced by LME49710/LME49600 is below the capabilities of all commercially available equipment. This makes distortion measurements just slightly more difficult than simply connecting a distortion meter to the amplifier's inputs and outputs. The solution, however, is quite simple: an additional resistor. Adding this resistor extends the resolution of the distortion measurement equipment.

The LME49710/LME49600's low residual distortion is an input referred internal error. As shown in Figure 27, adding the  $10\Omega$  resistor connected between the amplifier's inverting and non-inverting inputs changes the amplifier's noise gain. The result is that the error signal (distortion) is amplified by a factor of 101. Although the amplifier's closed-loop gain is unaltered, the feedback available to correct distortion errors is reduced by 101, which means that measurement resolution increases by 101. To ensure minimum effects on distortion measurements, keep the value of R1 low as shown in Figure 27.

This technique is verified by duplicating the measurements with high closed loop gain and/or making the measurements at high frequencies. Doing so produces distortion components that are within the measurement equipment's capabilities. This data sheet's THD+N and IMD values were generated using the above described circuit connected to an Audio Precision System Two Cascade.

Figure 27. THD+N Distortion Test Circuit

#### APPLICATION INFORMATION

#### HIGH PERFORMANCE, HIGH FIDELITY HEADPHONE AMPLIFIER

The LME49600 is the ideal solution for high output, high performance high fidelity head phone amplifiers. When placed in the feedback loop of the LME49710, LME49720 or LME49740 High Performance, High Fidelity audio operational amplifier, the LME49600 is able to drive  $32\Omega$  headphones to a dissipation of greater than 500mW at 0.00003% THD+N while operating on  $\pm 15$ V power supply voltages. The circuit schematic for a typical headphone amplifier is shown in Figure 28.

#### Operation

The following describes the circuit operation for the headphone amplifier's Left Channel. The Right Channel operates identically.

The audio input signal is applied to the input jack (HP31 or J1/J2) and dc-coupled to the volume control, VR1. The output signal from VR1's wiper is applied to the non-inverting input of U2-A, an LME49720 High Performance, High Fidelity audio operational amplifier. U2-A's AC signal gain is set by resistors R2, R4, and R6. To allow for a DC-coupled signal path and to ensure minimal output DC voltage regardless of the closed-loop gain, the other half of the U2 is configured as a DC servo. By constantly monitoring U2-A's output, the servo creates a voltage that compensates for any DC voltage that may be present at the output. A correction voltage is generated and applied to the feedback node at U2-A, pin 2. The servo ensures that the gain at DC is unity. Based on the values shown in Figure 28, the RC combination formed by R11 and C7 sets the servo's high-pass cutoff at 0.16Hz. This is over two decades below 20Hz, minimizing both amplitude and phase perturbations in the audio frequency band's lowest frequencies.

Figure 28. LME49600 Delivers High Output Current for this High Performance Headphone Amplifier

#### **AUDIO BUFFERS**

Audio buffers or unity-gain followers, have large current gain and a voltage gain of one. Audio buffers serve many applications that require high input impedance, low output impedance and high output current. They also offer constant gain over a very wide bandwidth.

Buffers serve several useful functions, either in stand-alone applications or in tandem with operational amplifiers. In stand-alone applications, their high input impedance and low output impedance isolates a high impedance source from a low impedance load.

#### SUPPLY BYPASSING

The LME49600 will place great demands on the power supply voltage source when operating in applications that require fast slewing and driving heavy loads. These conditions can create high amplitude transient currents. A power supply's limited bandwidth can reduce the supply's ability to supply the needed current demands during these high slew rate conditions. This inability to supply the current demand is further exacerbated by PCB trace or interconnecting wire inductance. The transient current flowing through the inductance can produce voltage transients.

For example, the LME49600's output voltage can slew at a typical  $\pm 2000 \text{V/µs}$ . When driving a  $100\Omega$  load, the di/dt current demand is 20 A/µs. This current flowing through an inductance of 50nH (approximately 1.5" of 22 gage wire) will produce a 1V transient. In these and similar situations, place the parallel combination of a solid  $5\mu\text{F}$  to  $10\mu\text{F}$  tantalum capacitor and a ceramic  $0.1\mu\text{F}$  capacitor as close as possible to the device supply pins.

Ceramic capacitors with values in the range of  $10\mu F$  to  $100\mu F$ , ceramic capacitor have very lower ESR (typically less than  $10m\Omega$ ) and low ESL when compared to the same valued tantalum capacitor. The ceramic capacitors, therefore, have superior AC performance for bypassing high frequency noise.

In less demanding applications that have lighter loads or lower slew rates, the supply bypassing is not as critical. Capacitor values in the range of 0.01µF to 0.1µF are adequate.

#### SIMPLIFIED LME49600 CIRCUIT DIAGRAM

The LME49600's simplified circuit diagram is shown in Figure 2. The diagram shows the LME49600's complementary emitter follower design, bias circuit and bandwidth adjustment node.

Figure 29 shows the LME49600 connected as an open-loop buffer. The source impedance and optional input resistor,  $R_S$ , can alter the frequency response. As previously stated, the power supplies should be bypassed with capacitors connected close to the LME49600's power supply pins. Capacitor values as low as  $0.01\mu F$  to  $0.1\mu F$  will ensure stable operation in lightly loaded applications, but high output current and fast output slewing can demand large current transients from the power supplies. Place a recommended parallel combination of a solid tantalum capacitor in the  $5\mu F$  to  $10\mu F$  range and a ceramic  $0.1\mu F$  capacitor as close as possible to the device supply pins.

Figure 29. Buffer Connections

#### **OUTPUT CURRENT**

The LME49600 can continuously source or sink 250mA. Internal circuitry limits the short circuit output current to approximately ±450mA. For many applications that fully utilize the LME49600's current source and sink capabilities, thermal dissipation may be the factor that limits the continuous output current.

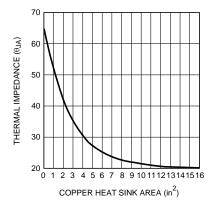

The maximum output voltage swing magnitude varies with junction temperature and output current. Using sufficient PCB copper area as a heat sink when the metal tab of the LME49600's surface mount TO–263 package is soldered directly to the circuit board reduces thermal impedance. This in turn reduces junction temperature. The PCB copper area should be in the range of 3in<sup>2</sup> (12.9cm<sup>2</sup>) to 6in<sup>2</sup> (38.7cm<sup>2</sup>).

#### THERMAL PROTECTION

LME49600 power dissipated will cause the buffer's junction temperature to rise. A thermal protection circuit in the LME49600 will disable the output when the junction temperature exceeds 150°C. When the thermal protection is activated, the output stage is disabled, allowing the device to cool. The output circuitry is enabled when the junction temperature drops below 150°C.

The TO–263 package has excellent thermal characteristics. To minimize thermal impedance, its exposed die attach paddle should be soldered to a circuit board copper area for good heat dissipation. Figure 30 shows typical thermal resistance from junction to ambient as a function of the copper area. The TO–263's exposed die attach paddle is electrically connected to the V<sub>FF</sub> power supply pin.

#### LOAD IMPEDANCE

The LME49600 is stable under any capacitive load when driven by a source that has an impedance of  $50\Omega$  or less. When driving capacitive loads, any overshoot that is present on the output signal can be reduced by shunting the load capacitance with a resistor.

# **OVERVOLTAGE PROTECTION**

If the input-to-output differential voltage exceeds the LME49600's Absolute Maximum Rating of 3V, the internal diode clamps shown in Figure 2 and conduct, diverting current around the compound emitter followers of Q1/Q5 (D1 - D7 for positive input), or around Q2/Q6 (D8 - D14 for negative inputs). Without this clamp, the input transistors Q1/Q2 and Q5/Q6 will zener and damage the buffer.

To ensure that the current flow through the diodes is held to a save level, the internal  $200\Omega$  resistor in series with the input limits the current through these clamps. If the additional current that flows during this situation can damage the source that drives the LME49600's input, add an external resistor in series with the input (see Figure 29).

## **BANDWITH CONTROL PIN**

The LME49600's –3dB bandwidth is approximately 110MHz in the low quiescent-current mode (7.3mA typical). Select this mode by leaving the BW pin unconnected.

Connect the BW pin to the  $V_{EE}$  pin to extend the LME49600's bandwidth to a nominal value of 180MHz. In this mode, the quiescent current increases to approximately 13.2mA. Bandwidths between these two limits are easily selected by connecting a series resistor between the BW pin and  $V_{EE}$ .

Regardless of the connection to the LME49600's BW pin, the rated output current and slew rate remain constant. With the power supply voltage held constant, the wide-bandwidth mode's increased quiescent current causes a corresponding increase in quiescent power dissipation. For all values of the BW pin voltage, the quiescent power dissipation is equal to the total supply voltage times the quiescent current ( $I_O$  \* ( $V_{CC}$  +  $|V_{EE}|$ )).

#### **BOOSTING OP AMP OUTPUT CURRENT**

When placed in the feedback loop, the LME49600 will increase an operational amplifier's output current. The operational amplifier's open loop gain will correct any LME49600 errors while operating inside the feedback loop.

To ensure that the operational amplifier and buffer system are closed loop stable, the phase shift must be low. For a system gain of one, the LME49600 must contribute less than 20° at the operational amplifier's unity-gain frequency. Various operating conditions may change or increase the total system phase shift. These phase shift changes may affect the operational amplifier's stability.

Unity gain stability is preserved when the LME49600 is placed in the feedback loop of most general-purpose or precision op amps. When the LME46900 is driving high value capacitive loads, the BW pin should be connected to the  $V_{\text{EE}}$  pin for wide bandwidth and stable operation. The wide bandwidth mode is also suggested for high speed or fast-settling operational amplifiers. This preserves their stability and the ability to faithfully amplify high frequency, fast-changing signals. Stability is ensured when pulsed signals exhibit no oscillations and ringing is minimized while driving the intended load and operating in the worst-case conditions that perturb the LME49600's phase response.

#### HIGH FREQUENCY APPLICATIONS

The LME49600's wide bandwidth and very high slew rate make it ideal for a variety of high-frequency open-loop applications such as an ADC input driver,  $75\Omega$  stepped volume attenuator driver, and other low impedance loads. Circuit board layout and bypassing techniques affect high frequency, fast signal dynamic performance when the LME49600 operates open-loop.

A ground plane type circuit board layout is best for very high frequency performance results. Bypass the power supply pins ( $V_{CC}$  and  $V_{EE}$ ) with  $0.1\mu F$  ceramic chip capacitors in parallel with solid tantalum  $10\mu F$  capacitors placed as close as possible to the respective pins.

Source resistance can affect high-frequency peaking and step response overshoot and ringing. Depending on the signal source, source impedance and layout, best nominal response may require an additional resistance of  $25\Omega$  to  $200\Omega$  in series with the input. Response with some loads (especially capacitive) can be improved with an output series resistor in the range of  $10\Omega$  to  $150\Omega$ .

#### THERMAL MANAGEMENT

#### Heatsinking

For some applications, the LME49600 may require a heat sink. The use of a heat sink is dependent on the maximum LME49600 power dissipation and a given application's maximum ambient temperature. In the TO-263 package, heat sinking the LME49600 is easily accomplished by soldering the package's tab to a copper plane on the PCB. (Note: The tab on the LME49600's TO-263 package is electrically connected to  $V_{\text{EE}}$ .)

Through the mechanisms of convection, heat conducts from the LME49600 in all directions. A large percentage moves to the surrounding air, some is absorbed by the circuit board material and some is absorbed by the copper traces connected to the package's pins. From the PCB material and the copper, it then moves to the air. Natural convection depends on the amount of surface area that contacts the air.

If a heat conductive copper plane has perfect thermal conduction (heat spreading) through the plane's total area, the temperature rise is inversely proportional to the total exposed area. PCB copper planes are, in that sense, an aid to convection. These planes, however, are not thick enough to ensure perfect heat conduction. Therefore, eventually a point of diminishing returns is reached where increasing copper area offers no additional heat conduction to the surrounding air. This is apparent in Figure 30 as the thermal resistance reaches an asymptote above a copper area of  $8\text{in}^2$ ). As can be seen, increasing the copper area produces decreasing improvements in thermal resistance. This occurs, roughly, at  $4\text{in}^2$  of 1 oz copper board. Some improvement continues until about  $16\text{in}^2$ . Boards using 2 oz copper boards will have decrease thermal resistance providing a better heat sink compared to 1 oz. copper. Beyond 1oz or 2oz copper plane areas, external heat sinks are required. Ultimately, the 1oz copper area attains a nominal value of  $20^\circ\text{C/W}$  junction to ambient thermal resistance ( $\theta_{\text{JA}}$ ) under zero air flow.

(1)

Figure 30. Thermal Resistance for 5-lead TO-263 Package Mounted on 1oz. Copper

A copper plane may be placed directly beneath the tab. Additionally, a matching plane can be placed on the opposite side. If a plane is placed on the side opposite of the LME49600, connect it to the plane to which the buffer's metal tab is soldered with a matrix of thermal vias per JEDEC Standard JESD51-5.

#### **Determining Copper Area**

Find the required copper heat sink area using the following guidelines:

- 1. Determine the value of the circuit's power dissipation, P<sub>D</sub>.

- 2. Specify a maximum operating ambient temperature,  $T_{A(MAX)}$ . (Note that the die temperature,  $T_J$ , will be higher than  $T_A$  by an amount that is dependent on the thermal resistance from junction to ambient,  $\theta_{JA}$ ). Therefore,  $T_A$  must be specified such that  $T_J$  does not exceed the absolute maximum die temperature of 150°C.

- 3. Specify a maximum allowable junction temperature,  $T_{J(MAX)}$ , This is the LME49600's die temperature when the buffer is drawing maximum current (quiescent and load). It is prudent to design for a maximum continuous junction temperature of 100°C to 130°C. Ensure, however, that the junction temperature never exceeds the 150°C absolute maximum rating for the part.

- 4. Calculate the value of junction to ambient thermal resistance,  $\theta_{JA}$

- 5.  $\theta_{JA}$  as a function of copper area in square inches is shown in Figure 30. Choose a copper area that will ensure the specified  $T_{J(MAX)}$  for the calculated  $\theta_{JA}$ . The maximum value of junction to ambient thermal resistance,  $\theta_{JA}$ , is defined as:

$$\theta_{JA} = (T_{J(MAX)} - T_{A(MAX)}) / P_{D(MAX)}$$

(°C/W)

#### where

- T<sub>J(MAX)</sub> = the maximum recommended junction temperature

- T<sub>A(MAX)</sub> = the maximum ambient temperature in the LME49600's environment

- P<sub>D(MAX)</sub> = the maximum recommended power dissipation

NOTE

The allowable thermal resistance is determined by the maximum allowable temperature increase:

$$T_{RISE} = T_{J(MAX)} - T_{A(MAX)}$$

Thus, if ambient temperature extremes force  $T_{RISE}$  to exceed the design maximum, the part must be de-rated by either decreasing  $P_D$  to a safe level, reducing  $\theta_{JA}$  further or, if available, using a larger copper area.

#### **Procedure**

1. First determine the maximum power dissipated by the LME49600,  $P_{D(MAX)}$ . For the simple case of the buffer driving a resistive load, and assuming equal supplies,  $P_{D(MAX)}$  is given by:

$$P_{DMAX(AC)} = (I_S \times V_S) + (V_S)^2 / (2\pi^2 R_L)$$

(Watts) (2)

$P_{DMAX(DC)} = (I_S \times V_S) + (V_S)^2 / R_L \text{ (Watts)}$

where

•  $V_S = |V_{EE}| + V_{CC}(V)$

Equation (2) is for sinusoidal output voltages and Equation (3) is for DC output voltages.

2. Determine the maximum allowable die temperature rise.

$$T_{RISE(MAX)} = T_{J(MAX)} - T_{A(MAX)} (^{\circ}C)$$

(4)

3. Using the calculated value of  $T_{RISE(MAX)}$  and  $P_{D(MAX)}$ , find the required value of junction to ambient thermal resistance combining Equation (1) and Equation (5) to derive Equation (9):

$$\theta_{\rm JA} = T_{\rm RISE(MAX)} / P_{\rm D(MAX)} \tag{5}$$

4. Finally, choose the minimum value of copper area from Figure 30 based on the value for  $\theta_{IA}$ .

#### **Example**

Assume the following conditions:  $V_S = |V_{EE}| + V_{CC} = 30V$ ,  $R_L = 32\Omega$ ,  $I_S = 15\text{mA}$ , sinusoidal output voltage,  $T_{J(MAX)} = 125^{\circ}\text{C}$ ,  $T_{A(MAX)} = 85^{\circ}\text{C}$ .

## Applying Equation (3):

$$P_{DMAX} = (I_S \times V_S) + (V_S)^2 / 2\pi^2 R_L$$

$$= (15\text{mA})(30\text{V}) + 900\text{V}^2 / 142\Omega$$

$$= 1.86\text{W}$$

(6)

#### Applying Equation (5):

$$T_{RISE(MAX)} = 125^{\circ}C - 85^{\circ}C$$

= 40°C (7)

#### Applying Equation (9):

$$\theta_{JA} = 40^{\circ}\text{C}/1.86\text{W}$$

= 21.5°C/W (8)

Examining the Copper Area vs.  $\theta_{JA}$  plot indicates that a thermal resistance of 50°C/W is possible with a  $12in^2$  plane of one layer of 1oz copper. Other solutions include using two layers of 1oz copper or the use of 2oz copper. Higher dissipation may require forced air flow. As a safety margin, an extra 15% heat sinking capability is recommended.

When amplifying AC signals, wave shapes and the nature of the load (reactive, non-reactive) also influence dissipation. Peak dissipation can be several times the average with reactive loads. It is particularly important to determine dissipation when driving large load capacitance.

The LME49600's dissipation in DC circuit applications is easily computed using Equation (4). After the value of dissipation is determined, the heat sink copper area calculation is the same as for AC signals.

#### **SLEW RATE**

A buffer's voltage slew rate is its output signal's rate of change with respect to an input signal's step changes. For resistive loads, slew rate is limited by internal circuit capacitance and operating current (in general, the higher the operating current for a given internal capacitance, the faster the slew rate).

However, when driving capacitive loads, the slew rate may be limited by the available peak output current according to the following expression.

$$dv/dt = I_{PK} / C_{I}$$

(9)

Output voltages with high slew rates will require large output load currents. For example if the part is required to slew at  $1000V/\mu s$  with a load capacitance of 1nF, the current demanded from the LME49600 is 1A. Therefore, fast slew rate is incompatible with a capacitive load of this value. Also, if  $C_L$  is in parallel with the load, the peak current available to the load decreases as  $C_L$  increases.

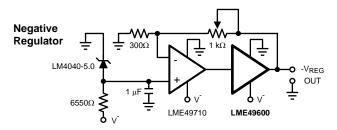

Figure 31. High Speed Positive and Negative Regulator

# **REVISION HISTORY**

| Rev  | Date     | Description                                        |  |  |  |  |

|------|----------|----------------------------------------------------|--|--|--|--|

| 1.0  | 01/15/08 | Initial release.                                   |  |  |  |  |

| 1.01 | 01/16/08 | Edited specification table.                        |  |  |  |  |

| 1.02 | 02/07/08 | Edited applications information.                   |  |  |  |  |

| 1.03 | 03/28/08 | Text edits.                                        |  |  |  |  |

| Е    | 04/04/13 | Changed layout of National Data Sheet to TI format |  |  |  |  |

## PACKAGE OPTION ADDENDUM

30-Jun-2016

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type     | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                 | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|------------------|--------------------|------|----------------|--------------------------|------------------|---------------------|--------------|----------------|---------|

| LME49600TS/NOPB  | ACTIVE | DDPAK/<br>TO-263 | KTT                | 5    |                | Pb-Free (RoHS<br>Exempt) | CU SN            | Level-3-245C-168 HR | -40 to 85    | LME49600<br>TS | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

30-Jun-2016

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic Security www.ti.com/security logic.ti.com

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity